2022年10月末、KiCad「Ver.6.0.9」がリリースされました。

今回の記事では、本バージョンアップについて、回路図エディタの修正点からいくつか気になった点を解説していきます。

全体的には今まで通り、バージョン6以降続けられているバグ除去作業が大半を占めています。これにより、回路図エディタ・PCBエディタとも、場合によっては大きな影響を及ぼす恐れのあったバグの解消も進んでいます。

なお、原文詳細につきましては、https://www.kicad.org/blog/2022/10/KiCad-6.0.9-Release/をご覧ください。

「共通項目」は開発寄りの修整が主体

まずは、改善点について、「General」共通項目の修正項目から2点ご紹介します。

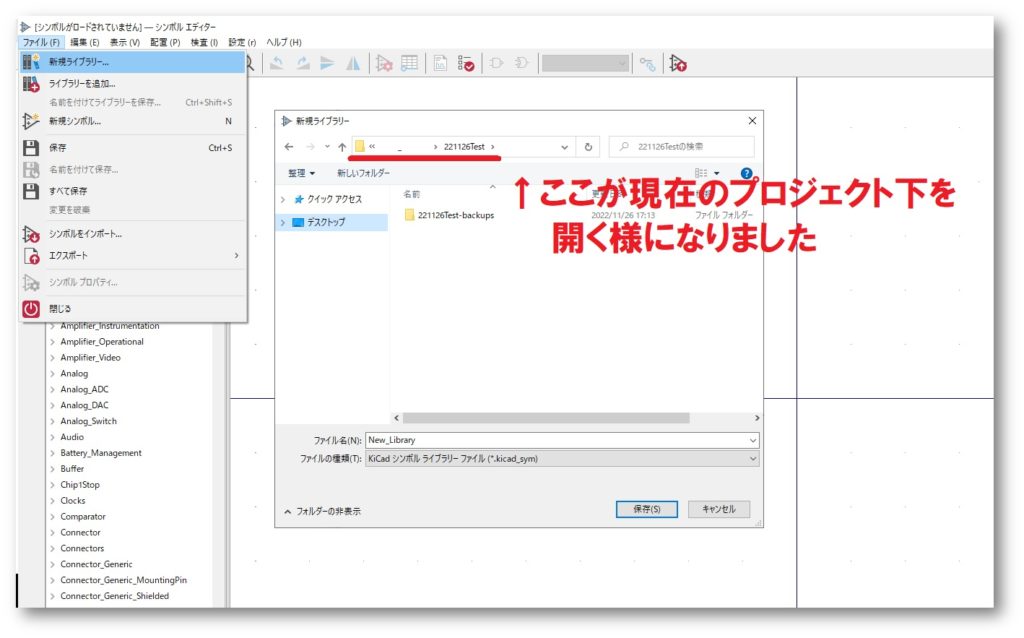

1点目は、「新規ライブラリーを作成する際、ひとつ前に開いたプロジェクトが開かれる」点が改善されました。

Ver.6.0.8までの操作では、現在開いているプロジェクトにて、シンボルエディタやフットプリントエディタで「新規ライブラリー」を選択すると、最初に開かれる場所がひとつ前に読み込んだプロジェクトフォルダの中となっていました。

「グローバル」および「プロジェクト」、いずれのライブラリーを選んだ場合であっても発生する現象は同じでしたが、アップデート後は現在開いているプロジェクトフォルダからスタートできるように変更されています。

筆者のブログ内では、独自ライブラリーを作成時はグローバル専用フォルダを指定し、そこへ集約することをオススメしています。

著者自身はこれまでの操作においても、新規ライブラリーを作成するメニューを選択した後、手動でロケーションを変更する癖がついていたため、最初に開くフォルダの場所についてあまり深刻に考えていませんでした。

しかし、

「基本名が同じプロジェクトファイルで、更新バージョンが複数ある」

「プロジェクトライブラリを多用する必要がある」

という使い方をされているユーザーの方の場合は、初期ロケーションの場所違いが原因になる問題を引き起こす可能性は十分に考えられます。

2点目は、「SWIG 4.1.0でのビルド失敗を起こす問題への修整」がなされた点です。

KiCadにはこれまでにもご紹介した通り、Pythonスクリプトを用いて様々な機能を自作して追加することができるようになっています。

普通にEDAとしての使用のみであれば、これまでのバージョンであっても影響は少なかったのですが、C/C++のプログラムをPythonに接続しより高度な処理を実現するプログラマーや開発チームそのものにとっては、ビルド失敗を起こす事象は重大な問題になっていました。

これはバグというよりは、開発環境のバージョンアップに伴う仕様変更が原因のようですが、最新のVer.6.0.9では解決しているそうです。

コミュニティ内でのやり取りを見ていると、開発チームはLinuxがメインなのかと思える記述もありますので、興味がある方はぜひコミュニティを覗いてみてください。

「回路図エディタ」の修正項目

回路図エディタにおいては、MacOS版による階層図面の表示ズレや、印刷やPDF出力時に表示項目が欠落する問題が修正されました。

多言語対応に関する問題では、ロシア語版の表示異常と中国語版の一部の動作不良が改善されています。これまで著者としては、海外とやり取りする場合はともかく、国内で留学生へKiCadを教えるときなどに経験していた問題であったため、改善されてよかったと思います。

正直「ERC実行時のエラー抜け対策」は微妙な印象

そして、回路図エディタの項目において、今回もっとも気になった点として「ERCの電源シンボルに関する修整」が行われたことについてご紹介します。

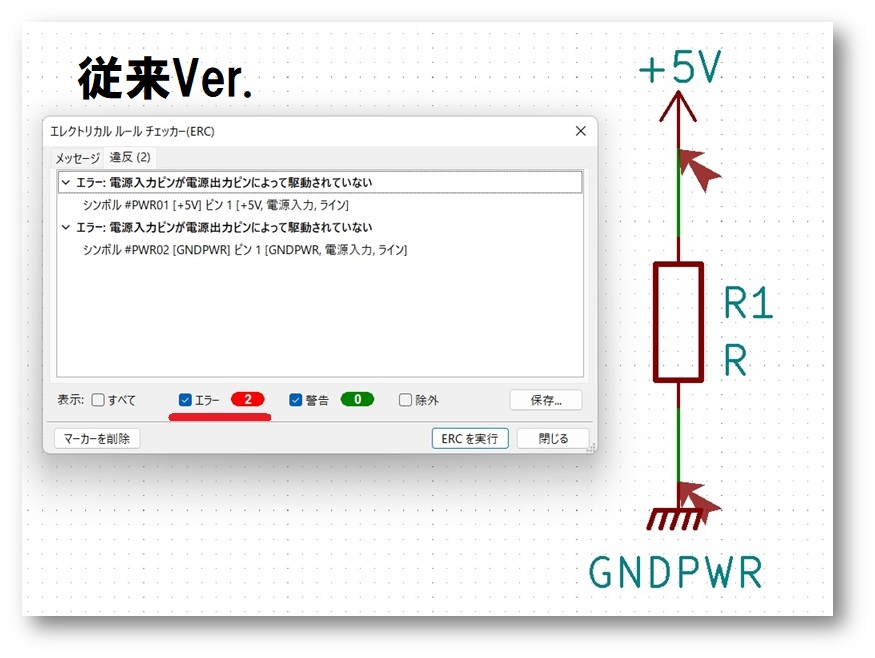

これまでのERCにおいても、電源入出力ピンに電源のシンボルが接続されていない場合、

「電源入力ピンが電源出力ピンによって駆動されていない」というエラーメッセージが表示されていました。

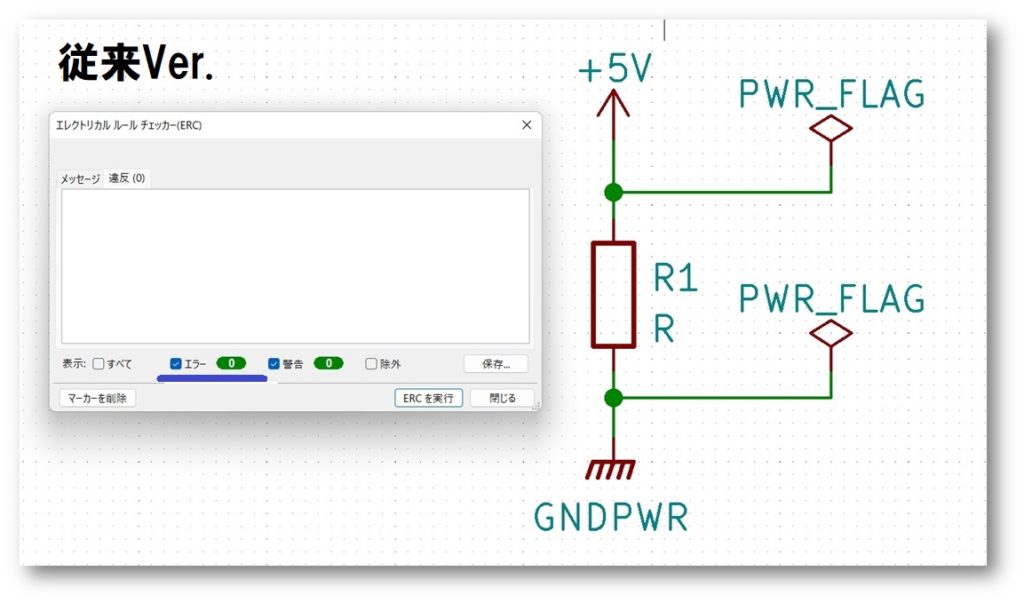

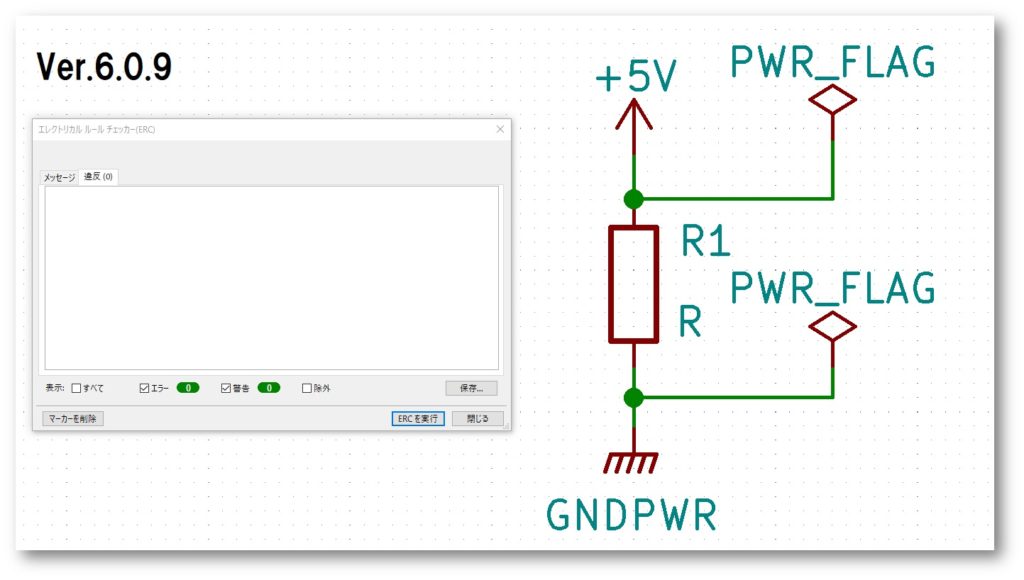

このエラーへの対策として、これまでは「POWER_FLAG」シンボルを接続することで回避してきました。

しかし、初めてEDAを扱う人などを中心に誤解して覚えてしまう人が増えてきているようです。そこで、従来バージョンでは、

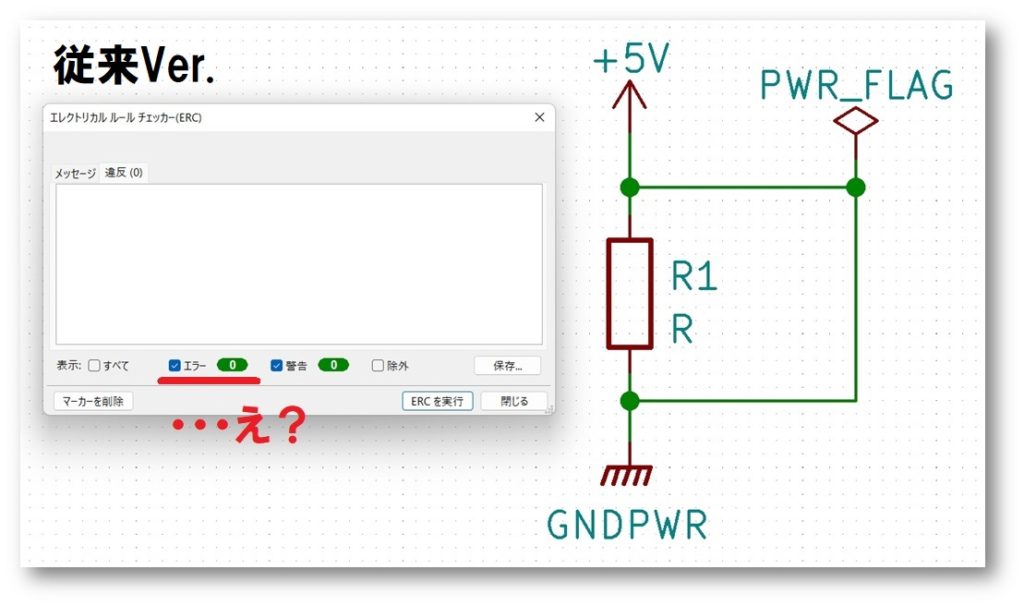

「ひとつの “PWR_FLAG” シンボルから、+とGND両方にワイヤーを接続してもERCが通過する」

という問題の発生が確認されていました。

「POWER_FLAG」は部品ではなく、「このラインは電源である」と宣言するラベルのようなものになっています。従って、PWR_FLAGから引き回されているワイヤーは、実際にはネットリストには発生しないはずです。

しかし、これが電源の+ラインとGNDを両方とも同じFLAGに接続すると、電源を短絡している線がネットリストに発生するリスクが生じます。

それにもかかわらず、従来バージョンでは、ERCによるチェックにてエラーにすることができずに通過してしまう状態でした。

最悪のケースとしては、回路図としての矛盾を無視し、「電源+とGNDを直結して、その中間にPWR_FLAGをつないだERC対策配線を作る」といった間違った描画も起こり得ます。

この点においては、KiCadの開発コミュニティにも記載されています。実際に筆者自身も、今まで開催したセミナーや学生対象の講習内で何度か目にしているため、その都度指導してきました。

回路設計を熟知している皆さんは、「そんなことは回路設計していればあたりまえのことでしょ」とおっしゃるかと思います。

しかし、「実際の回路に影響はないと“聞いているから”」と、本トラブルを誘発する描画をしている現役や若手技術者の方が意外と多いのです。

「そんなエラーも検出できないCADがおかしい!」

「そんなことにも気づかないエンジニアは未熟だ!」

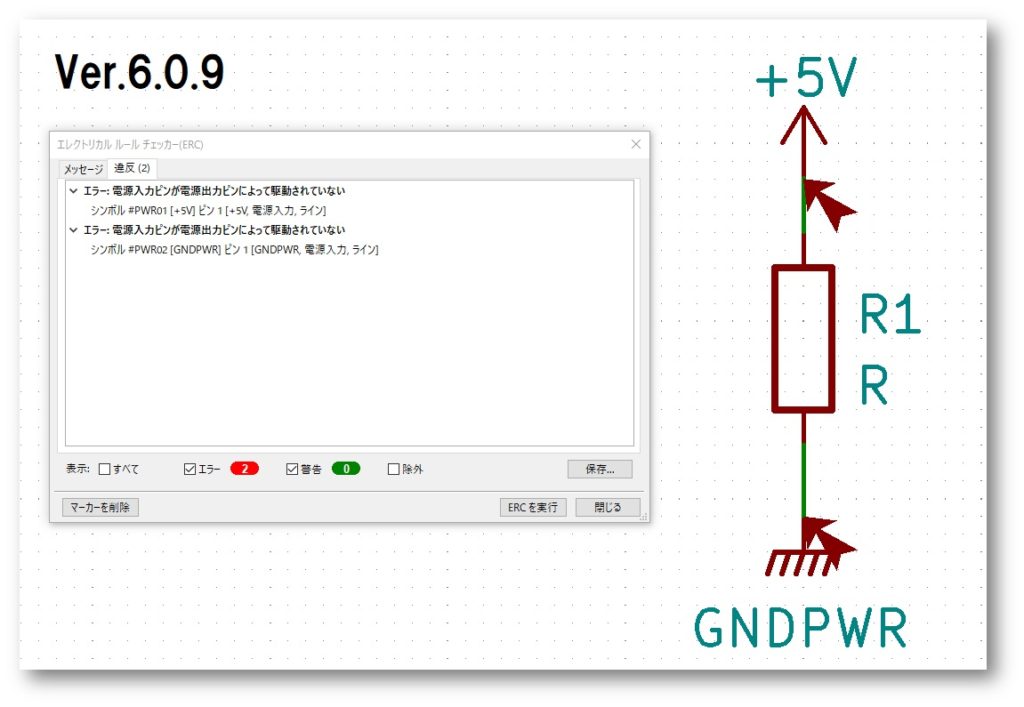

と、某チョコレート菓子論争のような争いも見られたこの問題ですが、ついにVer.6.0.9にて修正されました。

通常の処理については、今まで通りから特に変化はありません。

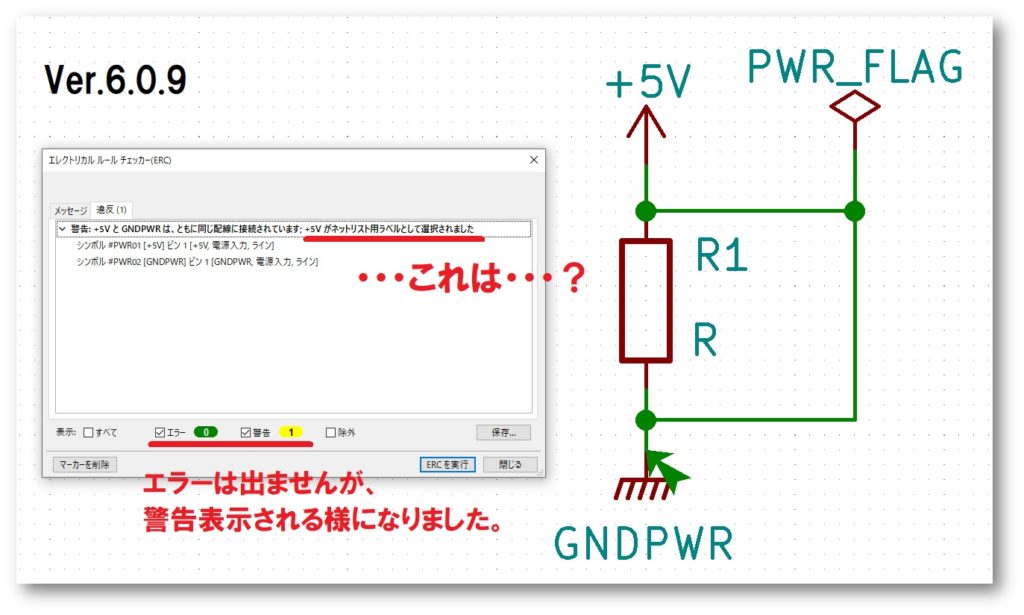

アップデート後に今回問題視している結線を行った場合には、警告メッセージが表示されるようになりました。

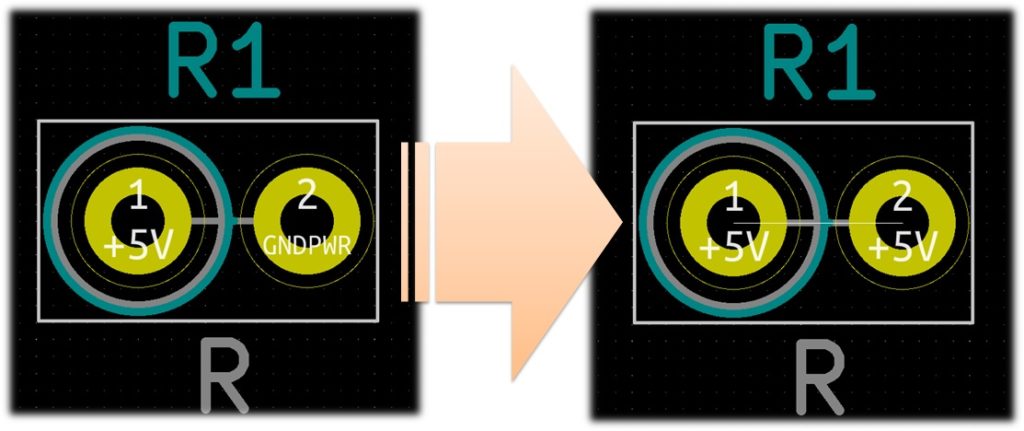

エラーではなく、「警告」表示が行われるだけに留まっていることに加え、さらにはネットラベルが自動的に割付変更されるという処理まで行われてしまっています。

この時点で警告表示が出ていることに気を留めて直してくるとありがたいのですが、もしも警告表示のチェックをOFFにしたままであったり、このまま修正せずPCBエディタに移行した場合には、ネットラベルの処理は正常に行われません。

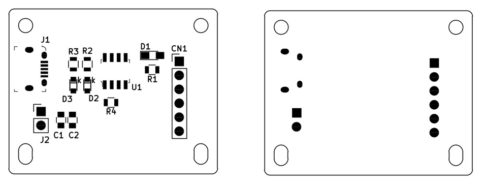

上図の場合には、「+5V」がネットラベルとして選択され処理されたため、抵抗のフットプリント両端が「+5V」となり、短絡するように補助線が誘導されてしまっています。

これはデバッグのつもりで新たなバグを生んだだけなのではないだろうか・・・。

KiCadユーザーの皆さんは、ERCで警告が表示された場合には、決して軽視せず必ず回路を修整するように心がけましょう。

PCBエディタの更新情報は別途

今回の記事では、回路図エディタの修正項目についてご紹介しました。

なお、PCBエディタについては、更新項目がすごいことになっています。改めて別記事にてご紹介したいと思いますので、更新のチェックをお願いいたします。